# Ruttonsha International Rectifier Ltd.

## SILICON CONTROLLED RECTIFIERS

# 41RIA, 51RIA SERIES Power Silicon Controlled Rectifiers 64, 80 Amp RMS SCRs

Types: 41RIA10-41RIA140, 51RIA10-51RIA140

#### **FEATURES**

- ∉ All diffused series.

- ∉ High di/dt and dv/dt capabilities.

- # Reliable blocking at elevated temperature.

- ∉ High surge current rating.

- *∉* High I²t capability.

- *∉* Excellent dynamic characteristics.

#### THERMAL MECHANICAL SPECIFICATIONS

| R <sub>thjc</sub> | Maximum thermal resistance junction-to-case | 41RIA                          | 51RIA    |  |

|-------------------|---------------------------------------------|--------------------------------|----------|--|

|                   | DC operation                                | 0.4°C/W                        | 0.35°C/W |  |

| R <sub>thcs</sub> | Contact thermal resistance case-to-sink     | 0.25°C/W                       |          |  |

| T <sub>J</sub>    | Junction operating temp. range              | -40°C to +125°C                |          |  |

| T <sub>stg</sub>  | Storage temperature range                   | -40°C to +                     | -125ºC   |  |

|                   | Mounting torque<br>(Non-lubricated threads) | 0.4 M-Kg min.<br>0.6 M-Kg max. |          |  |

|                   | Approximate weight                          | 30 gms.                        |          |  |

#### **ELECTRICAL RATINGS**

| TYPE                              | 41RIA / 51RIA                                                                               | 10  | 20  | 40  | 60  | 80  | 100  | 120  | 140  |

|-----------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|------|------|------|

| V <sub>DRM</sub>                  | Max. repetitive peak off state voltage (V)                                                  | 100 | 200 | 400 | 600 | 800 | 1000 | 1200 | 1400 |

| $V_{RRM}$                         | Max. repetitive peak reverse voltage (V)                                                    | 100 | 200 | 400 | 600 | 800 | 1000 | 1200 | 1400 |

| V <sub>RSM</sub>                  | Max. non-repetitive peak reverse voltage (V)                                                | 150 | 300 | 500 | 700 | 900 | 1100 | 1300 | 1500 |

| I <sub>RM</sub> & I <sub>DM</sub> | Max. peak reverse & off state current @ rated V <sub>DRM</sub> & V <sub>RRM</sub> 125°C -mA | 15  | 15  | 15  | 15  | 15  | 15   | 15   | 15   |

## **SILICON CONTROLLED RECTIFIERS**

## 41 RIA, 51 RIA SERIES

### **ELECTRICAL SPECIFICATIONS**

|                     | ON-STATE                                                                                | 41RIA            | 51RIA                    | Units                                | Conditions                                                                                                                                                    |                                                                                                    |  |  |

|---------------------|-----------------------------------------------------------------------------------------|------------------|--------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| I <sub>T(RMS)</sub> | Max. RMS on-state current                                                               | 65               | 80                       | Α                                    |                                                                                                                                                               |                                                                                                    |  |  |

| I <sub>T(AV)</sub>  | Max. average on-state current                                                           | 40               | 50                       | Α                                    | T <sub>c</sub> = 94°C max., 180°C sir                                                                                                                         | nusoidal conduction.                                                                               |  |  |

| I <sub>TSM</sub>    | Max. peak one cycle non-repetitive surge current                                        | 1050             | 1200                     | A                                    | 50 Hz half cycle sine<br>wave or 6 ms rectangular                                                                                                             | Following any rated load conditions and with rated $V_{\mbox{\tiny RRM}}$ applied following surge. |  |  |

|                     |                                                                                         | 1250             | 1430                     |                                      | pulse.                                                                                                                                                        | Following any rated load condition and with no voltage reapplied following surge.                  |  |  |

| l²t                 | Max. I <sup>2</sup> t capability for fusing                                             | 5700             | 7200                     | A²s                                  | t = 10 ms Ra                                                                                                                                                  | ns Rated $V_{RRM}$ applied following surge, initial $T_J = 125^{\circ}C$                           |  |  |

| l²t                 | Max. I²t capability for individual (1) device fusing                                    | 8060             | 10180                    | A²s                                  | t = 10 ms V <sub>F</sub>                                                                                                                                      | t = 10 ms $V_{RRM}$ following surge = 0, initial $T_J$ = 125°C                                     |  |  |

| I²√t                | Max. $I^2\sqrt{t}$ capability for individual device fusing                              | 80600            | 101800                   | A²√s                                 | t = 0.1 to 10 ms V, in                                                                                                                                        | $_{RRM}$ following surge = 0,, itial $T_J$ = 125°C                                                 |  |  |

| V <sub>TM</sub>     | Max. peak on-state voltage                                                              | 1.65             | 1.6                      | V                                    | $T_{J} = 25^{\circ}C, I_{TM} = \pi \times I_{T(AV)}$                                                                                                          |                                                                                                    |  |  |

| I <sub>H</sub>      | Max. holding current                                                                    | 20               | 00                       | mA                                   | $T_J = 25^{\circ}$ C, anode supply = 22V, initial $I_T = 2.0$ A                                                                                               |                                                                                                    |  |  |

| I <sub>L</sub>      | Max. latching current                                                                   | 40               | 00                       | mA                                   | Anode supply = 6V, resistive load.                                                                                                                            |                                                                                                    |  |  |

| BLOC                | KING                                                                                    |                  | (1) I <sup>2</sup> t for | time t <sub>x</sub> = I <sup>2</sup> | <sup>2</sup> √t * √t,                                                                                                                                         |                                                                                                    |  |  |

| dv/dt               | Min. critical rate-of-rise of off-state voltage                                         | 20               | 00                       | V/μs<br>-                            | $T_J = 125^{\circ}$ C. Exponential Zero gate bias voltage to 100% rated $V_{DPM}$ gate open circuited.                                                        |                                                                                                    |  |  |

| 0)4//ТО             | LUNG                                                                                    | 50               | 00                       |                                      | For 67% rated V                                                                                                                                               |                                                                                                    |  |  |

| SWITC               | HING                                                                                    |                  | 1                        |                                      | Ι                                                                                                                                                             |                                                                                                    |  |  |

| t <sub>d</sub>      | Typical delay time                                                                      | 0.               | 9                        | μs                                   | $T_{\rm C}$ = 25°C, $V_{\rm DM}$ = rated $V_{\rm DRM}$ , $I_{\rm TM}$ = 10A dc resistive circuit, Gate pulse 10V, 15 $\Omega$ source $t_{\rm p}$ = 20 $\mu$ S |                                                                                                    |  |  |

| di/dt               | Max non-repetitive rate of rise of turned-on current $V_{RRM}$ = 700- 1400 V 50 - 600 V | 20               | 00                       | A/μs                                 | $T_{\rm C}$ = 125°C, $V_{\rm DM}$ = rated $V_{\rm DRM}$ , $I_{\rm TM}$ = 2 x rated di/dt. Gate pulse 20V, 15Ω, $t_{\rm p}$ = 6 μS, $t_{\rm r}$ = 0.1 μS max.  |                                                                                                    |  |  |

| t <sub>q</sub>      | Typical turn-off time                                                                   | 11               | 0                        | μs                                   | T <sub>c</sub> = 125°C, I <sub>TM</sub> = 50A, di                                                                                                             | /dt = 10 A/μS, V <sub>R</sub> during turn-off<br><del>llied dv/dt = 20 V/μS linear to</del>        |  |  |

| TRIGG               | ERING                                                                                   |                  |                          |                                      | rated V <sub>DRM</sub> Gate bias : 0V                                                                                                                         | , $100\Omega$                                                                                      |  |  |

| P <sub>GM</sub>     | Max. peak gate power                                                                    | 1                | 0                        | W                                    | tp ≤ 5ms                                                                                                                                                      |                                                                                                    |  |  |

| $P_{G(AV)}$         | Max. average gate power                                                                 | 2.               | 5                        | W                                    |                                                                                                                                                               |                                                                                                    |  |  |

| I <sub>GM</sub>     | Max. peak positive gate current                                                         | 2.               | 5                        | Α                                    |                                                                                                                                                               |                                                                                                    |  |  |

| +V <sub>GM</sub>    | Max. peak positive gate voltage                                                         | 2                | 0                        | V                                    |                                                                                                                                                               |                                                                                                    |  |  |

| -V <sub>GM</sub>    | Max. peak negative gate voltage                                                         | 1                | 0                        | V                                    |                                                                                                                                                               |                                                                                                    |  |  |

| I <sub>GT</sub>     | Max. required DC gate current to trigger                                                | 250<br>100<br>50 |                          | mA                                   |                                                                                                                                                               | required gate trigger current is the                                                               |  |  |

|                     | 35                                                                                      |                  |                          |                                      | $T_{\rm J} = 125^{\circ}$ C with + 6V anode-to-cathode.                                                                                                       |                                                                                                    |  |  |

| V <sub>GT</sub>     | Max. required DC gate voltage                                                           | 3.5              |                          | V                                    | $T_J = -40^{\circ}C$ Max.                                                                                                                                     | required gate trigger voltage is the                                                               |  |  |

|                     | to trigger                                                                              |                  |                          |                                      |                                                                                                                                                               | 6V anode-to-cathode.                                                                               |  |  |

| V <sub>GD</sub>     | Max. DC gate voltage not to trigger                                                     | 0.               | 2                        | V                                    |                                                                                                                                                               | gate current or voltage not to trigger is aximum value which will not trigger any                  |  |  |

| I <sub>GD</sub>     | Max. DC gate current not to trigger                                                     | 5.               | 0                        | mA                                   |                                                                                                                                                               | unit with rated V <sub>DRM</sub> anode-to-cathode.                                                 |  |  |

# SILICON CONTROLLED RECTIFIERS

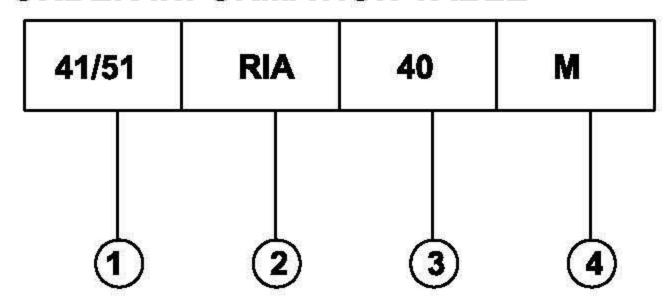

# **ORDER INFORMATION TABLE**

- (1) Current Code

- 40/50 without external lead 41/51 - with external lead

- (2) RIA Essential part number

- Voltage Rating (See table)

- None Stud 1/4" 28UNF 2A Threading

M Stud M8 x 1.25P Metric Threading

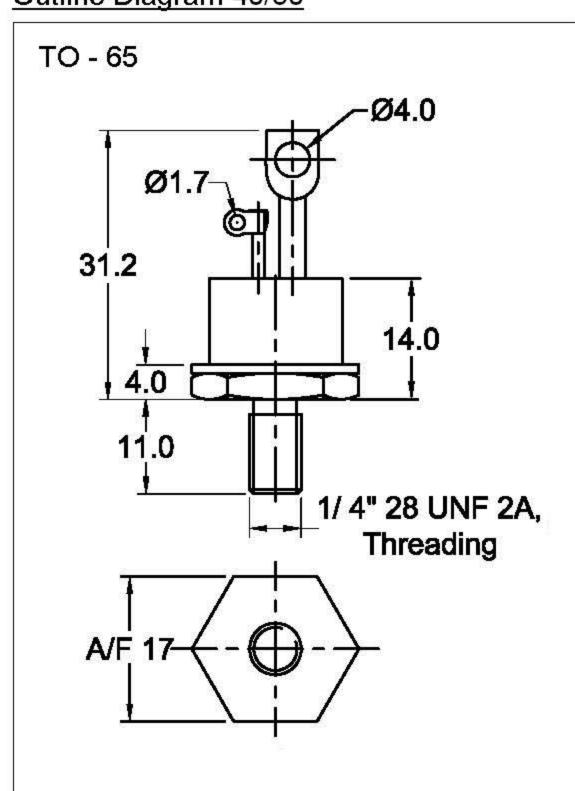

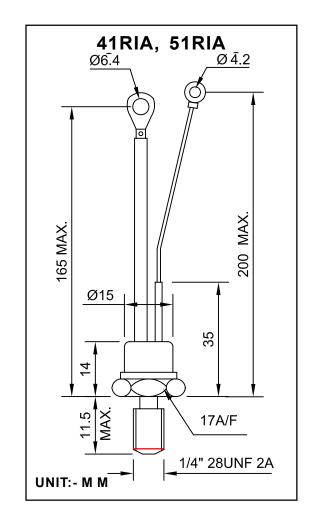

## Outline Diagram 40/50